If desired, move the pins to different locations on the symbol by dragging and dropping names from one box to another.For the Destination selection, choose “Create a new symbol with the specified model attached.” The dialog box should appear as follows:.For the Source selection, choose “Create a new, empty model.”.Select the Model Wizard command in the VHDL menu.Select the New command in the File menu, and then double-click on the VHDL selection.First, close any open circuit diagrams or VHDL files.We’ll also take the opportunity to use vectors, or multibit signals. We’ll now look at how we can use VHDL to describe the operation of a device that is going to be used in a LogicWorks circuit diagram. This delay is due to the AFTER 1 NS specification in the VHDL model.Ĭreating a VHDL Model for a Device Symbol Note that there is a 1-ns delay between input changes and the corresponding output change. Now try changing the input values again, and watch the effect in the timing diagram.You could also have done this to the Timing tab, if desired. This command places the I/O Panel in a separate, floating window so that you can view both at the same time. If the name IOPanelDefault.html is not already displayed, click on the list and choose the item ending with IOPanelDefault.html. Check the selection list at the top of the I/O Panel.Note: If the I/O Panel has already been used, you might need to click the I/O Panel tab in the Results Panel in order to bring it to the top.

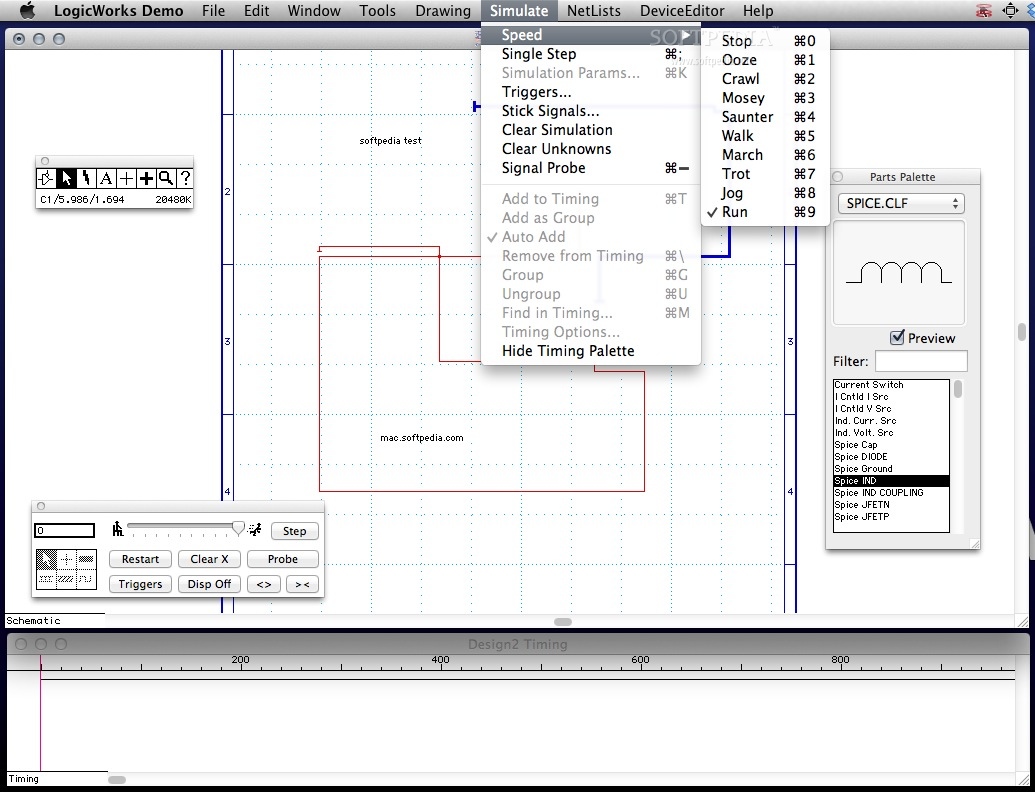

This will cause a new panel to be displayed in the results area at the bottom of the screen. Now we need a method of feeding inputs into our design and checking the outputs. You will now see the VHDL text document turn gray to indicate that it cannot be edited while the simulation is running. Click the Run ( ) button to start the simulator.Locate the line that starts - Your VHDL code, and replace it with.You should receive a warning that output OUT1 has not been assigned You will notice that a new panel appears at the bottom of the screen with the compilation results. Go to the VHDL menu and select the Compile command.Before we proceed, we must verify that this is a correct VHDL file. We now have a complete VHDL description of a component having the desired inputs and outputs, except that no code has been added to describe the actual behaviour of the device. –Your VHDL code defining the model goes here You should now see a new document window open containing text like this: Click the Finish button to create the model file.IMPORTANT: The settings in the Func column must appear as shown above! Enter the name OUT1, and click the Add Single Bit button.Go back to the top of the panel and change the Function selection to Output.Enter the name NEG, and click the Add Single Bit button again to add the second input.The note above about names in VHDL applies also to input and output names, so you have to be sure to use something that isn’t a reserved word. Enter the name POS for the first input.Set the function to Input, if it is not already.In this case, we wish to add two single-bit inputs and one single-bit output. We now specify the “interface” to the model, that is, what its inputs and outputs will be. For example, AND would not be a valid name. Note: Since this name will be used in the VHDL source file, you cannot use a VHDL reserved keyword or anything containing invalid characters as a name. Enter a name for the new model, such as AND1INV.Therefore, an XNOR gate is true only when the two inputs are the same. The XNOR gate follows the same conventions as above, and acts like an XOR gate whose output is then fed into a NOT gate. For example, the two inputs '1' and '0' would produce a true ('1') output, but the two inputs '1' and '1' or '0' and '0' would produce a false ('0') output (this is conventionally named "exclusive or"). The XOR gate is true when the inputs are opposite of each other, but false when they are equal. Therefore, it is true only in the case where both inputs are zeroes (the only case that would have made an OR gate output a '0'). The NOR gate is essentially an OR gate whose output is then fed into a NOT gate. Therefore, it is true in all cases except for when both inputs are '1'. The NAND gate is essentially an AND gate whose output is then fed into a NOT gate. it will flip a '1' to a '0' and a '0' to a '1'). The NOT gate takes in one input and inverts that input (i.e. The OR gate takes two inputs and evaluates to true when either one of its inputs are true (or if both inputs are true - this is conventionally named "inclusive or"). outputs a '1') when both of its inputs are true, or false otherwise. The AND gate takes two inputs and evaluates to true (i.e. The logic gates include: AND, OR, NOT, NAND, NOR, XOR and XNOR. These gates are used in combinational and sequential circuit design. You have a multitude of different logic gates that operate within a computer.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed